모든 RTL 하드웨어 디자인 팀이 알아야 하는 것

| 일 정 | 2021-02-17 10:30 ~ 12:00 |

|---|---|

| 회 사 명 | SIEMENS EDA |

| 발 표 자 | 이준석차장/시니어 애플리케이션 엔지니어 |

| 경 품 명 | 앵콜 세미나 |

세미나 등록/참가

종료된 세미나입니다.

세미나 다시보기

세미나 설명

이 세미나는,

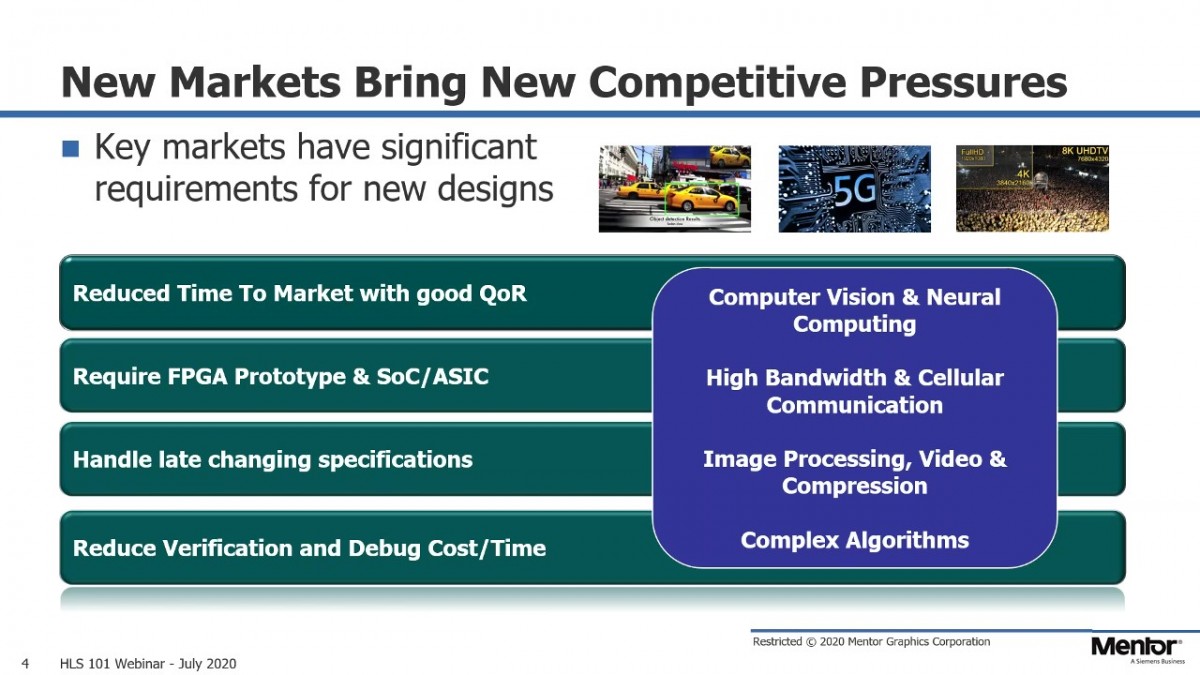

최근 컴퓨터 비전, 인공지능 머신러닝, 5G 통신 같은 응용분야에서는 상당히 복잡한 알고리즘이 필요합니다. 수만 수십만의 연산과 메모리 엑세스를 하드웨어로 아키텍처링하고 이를 수작업 코딩하여 하드웨어로 디자인 하는 것은 매우 어려운 일일 것입니다.

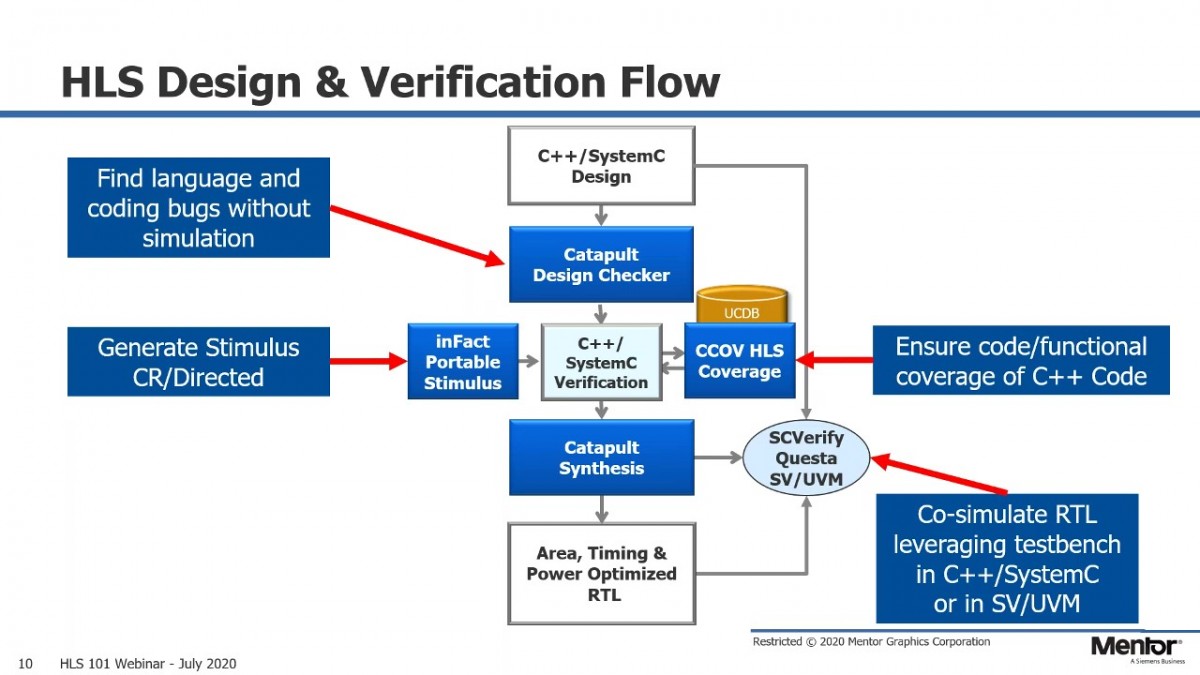

캐타펄트 HLS 솔루션은 C++/SystemC와 같은 상위수준언어를 입력으로 RTL을 구현합니다. 합성 가능한 디자인을 입력하고 설계자는 동작 주파수, 클럭, 리셋, 사용할 메모리의 종류와 같은 하드웨어 제약사항을 툴에 적용합니다.

본 웹 세미나에서 HLS에 대한 간략한 소개와 함께 어떻게 HLS을 활용하여 설계 기간을 단축시키고 그 만큼 검증에 투자하는 시간을 늘려 보다 완성도 있는 하드웨어 설계를 만들어 낼 수 있는지 알아봅니다.